ARTIX-7 FPGA

اصلي بورډ

AC7A200

په موډل کې سیسټم

د کارن لارښود

نسخه ریکارډ

| نسخه | نیټه | لخوا خوشې کول | تفصیل |

| ریو 1.0 | 28-06-20 | راحیل ژو | لومړی خوشې کول |

برخه 1: د AC7A200 کور بورډ پیژندنه

AC7A200 (د اصلي بورډ ماډل، لاندې ورته ورته) د FPGA کور بورډ، دا د XILINX د ARTIX-7 لړۍ 100T XC7A200T-2FBG484I پر بنسټ والړ دی. دا د لوړ سرعت، لوړ بینډ ویت او لوړ ظرفیت سره د لوړ فعالیت اصلي بورډ دی. دا د لوړ سرعت ډیټا مخابراتو ، د ویډیو عکس پروسس کولو ، د تیز سرعت ډیټا استملاک وغيره لپاره مناسب دی.

دا AC7A200 کور بورډ د مایکرون د MT41J256M16HA-125 DDR3 چپ دوه ټوټې کاروي، هر DDR د 4Gbit ظرفیت لري؛ دوه DDR چپس د 32-bit ډیټا بس چوکۍ کې یوځای شوي، او د FPGA او DDR3 ترمنځ د لوستلو / لیکلو ډاټا بینډ ویت تر 25Gb پورې دی؛ دا ډول ترتیب کولی شي د لوړ بینډ ویت ډیټا پروسس کولو اړتیاوې پوره کړي.

د AC7A200 کور بورډ د 180V کچې 3.3 معیاري IO بندرونه ، د 15V کچې 1.5 معیاري IO بندرونه ، او د GTP لوړ سرعت RX/TX توپیر سیګنالونو 4 جوړه پراخه کوي. د کاروونکو لپاره چې ډیری IO ته اړتیا لري، دا اصلي بورډ به یو ښه انتخاب وي. سربیره پردې ، د FPGA چپ او انٹرفیس ترمینځ روټینګ مساوي اوږدوالی او توپیر پروسس کوي ، او د اصلي بورډ اندازه یوازې 2.36 انچ * 2.36 انچ ده ، کوم چې د ثانوي پراختیا لپاره خورا مناسب دی.

شکل 1-1: AC7A200 کور بورډ (مخکې View)

شکل 1-2: AC7A200 کور بورډ (شاته View)

برخه 2: FPGA چپ

لکه څنګه چې پورته یادونه وشوه، د FPGA ماډل چې موږ یې کاروو XC7A200T-2FBG484I دی، کوم چې د Xilinx Artix-7 لړۍ پورې اړه لري. د سرعت درجه 2 ده، او د حرارت درجه د صنعت درجه ده. دا ماډل د 484 پنونو سره د FGG484 کڅوړه ده. د Xilinx ARTIX-7 FPGA چپ نومولو قواعد په لاندې ډول دي

شکل 2-1: د ARTIX-7 لړۍ ځانګړي چپ ماډل تعریف

شکل 2-2: په تخته کې د FPGA چپ

د FPGA چپ XC7A200T اصلي پیرامیټونه په لاندې ډول دي

| نوم | ځانګړي پیرامیټونه |

| د منطق حجرې | 215360 |

| ټوټې | 16-02-92 |

| CLB فلیپ فلاپ | 269200 |

| بلاک رام (kb) | 13140 |

| د DSP ټوټې | 740 |

| PCIe Gen2 | 1 |

| XADC | 1 XADC، 12bit، 1Mbps AD |

| د GTP لیږدونکی | 4 GTP، 6.6Gb/s اعظمي |

| د سرعت درجه | -2 |

| د حرارت درجه | صنعتي |

د FPGA بریښنا رسولو سیسټم

د آرټیکس-7 FPGA بریښنا تجهیزات VCCINT، VCCBRAM، VCCAUX، VCCO، VMGTAVCC او VMGTAVTT دي. VCCINT د FPGA اصلي بریښنا رسولو پن دی، کوم چې اړتیا لري د 1.0V سره وصل شي؛ VCCBRAM د FPGA بلاک رام د بریښنا رسولو پن دی، له 1.0V سره وصل دی؛ VCCAUX د FPGA معاون بریښنا رسولو پن دی، 1.8V سره نښلوي؛ VCCO د والیت دیtagد FPGA د هر بانک e، په شمول د BANK0، BANK13~16، BANK34~35. په AC7A200 FPGA کور بورډ کې، BANK34 او BANK35 باید د DDR3 سره وصل شي، حجمtagد بانک e ارتباط 1.5V دی، او حجمtagد نورو بانکونو e 3.3V دی. د BANK15 او BANK16 VCCO د LDO لخوا پرمخ وړل کیږي، او د LDO چپ په ځای کولو سره بدلیدلی شي. VMGTAVCC د عرضې حجم دیtagد FPGA داخلي GTP ټرانسیور e، د 1.0V سره وصل شوی؛ VMGTAVTT د ختمولو حجم دیtagد GTP ټرانسیور e، د 1.2V سره وصل شوی.

د Artix-7 FPGA سیسټم ته اړتیا لري چې د بریښنا پورته کولو ترتیب د VCCINT، بیا VCCBRAM، بیا VCCAUX، او په پای کې VCCO لخوا بریښنا وي. که VCCINT او VCCBRAM ورته والی ولريtage، دوی کولی شي په ورته وخت کې ځواکمن شي. د واک ترتیب outages بیرته راګرځي. د GTP ټرانسیور د بریښنا پورته کولو ترتیب VCCINT دی، بیا VMGTAVCC، بیا VMGTAVTT. که VCCINT او VMGTAVCC ورته والی ولريtage، دوی کولی شي په ورته وخت کې ځواکمن شي. د بریښنا بند ترتیب یوازې د بریښنا د ترتیب سره مخالف دی.

دریمه برخه: فعال توپیري کرسټال

د AC7A200 کور بورډ د دوه سایټیم فعال توپیري کرسټالونو سره مجهز دی، یو یې 200MHz دی، ماډل یې SiT9102-200.00MHz دی، د FPGA لپاره د سیسټم اصلي ساعت او د DDR3 کنټرول ساعت تولید لپاره کارول کیږي؛ بل یې 125MHz دی، ماډل SiT9102 -125MHz دی، د GTP لیږدونکو لپاره د حوالې ساعت ان پټ.

برخه 3.1: 200Mhz فعال توپیر ساعت

په 1-3 شکل کې G1 د 200M فعال توپیر کرسټال دی چې د پراختیا بورډ سیسټم ساعت سرچینه چمتو کوي. د کرسټال محصول د FPGA د BANK34 نړیوال ساعت پن MRCC (R4 او T4) سره وصل دی. دا د 200Mhz توپیر ساعت په FPGA کې د کارونکي منطق چلولو لپاره کارول کیدی شي. کاروونکي کولی شي PLLs او DCMs د FPGA دننه تنظیم کړي ترڅو د مختلف فریکونسیو ساعتونه تولید کړي.

شکل 3-1: 200Mhz فعال توپیري کرسټال سکیماټیک

شکل 3-2: په کور بورډ کې 200Mhz فعال توپیري کرسټال

د 200Mhz توپیري ساعت پن دنده

| د سیګنال نوم | د FPGA پن |

| SYS_CLK_P | R4 |

| SYS_CLK_N | T4 |

برخه 3.2: 125MHz فعال توپیري کرسټال

په 2-3 شکل کې G3 د 125MHz فعال توپیر کرسټال دی، کوم چې د حوالې ان پټ ساعت دی چې د FPGA دننه GTP ماډل ته چمتو شوی. د کرسټال محصول د FPGA د GTP BANK216 ساعت پنونو MGTREFCLK0P (F6) او MGTREFCLK0N (E6) سره وصل دی.

شکل 3-3: 125MHz فعال توپیر لرونکي کرسټال سکیماتیک

شکل 3-4: په کور بورډ کې 125MHz فعال توپیري کرسټال

د 125MHz توپیري ساعت پن دنده

| خالص نوم | د FPGA پن |

| MGT_CLK0_P | F6 |

| MGT_CLK0_N | E6 |

دریمه برخه: DDR4 DRAM

د FPGA کور بورډ AC7A200 د دوه مایکرون 4Gbit (512MB) DDR3 چپس (په بشپړ ډول 8Gbit) سره مجهز دی، ماډل یې MT41J256M16HA-125 دی (د MT41K256M16HA-125 سره مطابقت لري). د DDR3 SDRAM اعظمي عملیاتي سرعت 400MHz (د معلوماتو کچه 800Mbps) لري. د DDR3 حافظه سیسټم مستقیم د FPGA د بانک 34 او BANK35 د حافظې انٹرفیس سره وصل دی. د DDR3 SDRAM ځانګړی ترتیب په جدول 4-1 کې ښودل شوی.

| د بټ شمیره | چپ موډل | ظرفیت | فابریکه |

| U5,U6 | MT41J256M16HA-125 | 256M x 16bit | مایکرون |

جدول 4-1: د DDR3 SDRAM ترتیب

د DDR3 هارډویر ډیزاین د سیګنال بشپړتیا سخت غور ته اړتیا لري. موږ په بشپړ ډول د مطابقت مقاومت / ټرمینل مقاومت په پام کې نیولی دی، د خنډ کنټرول ټریس، او د سرکټ ډیزاین او PCB ډیزاین کې د اوږدوالي کنټرول تعقیب ترڅو د DDR3 لوړ سرعت او مستحکم عملیات یقیني کړي. شکل 4-1 د DDR3 DRAM هارډویر پیوستون توضیح کوي

شکل 4-1: د DDR3 DRAM سکیماتیک

شکل 4-2: DDR3 په کور بورډ کې

د DDR3 DRAM پن دنده:

| خالص نوم | د FPGA PIN نوم | FPGA P/N |

| DDR3_DQS0_P | IO_L3P_T0_DQS_AD5P_35 | E1 |

| DDR3_DQS0_N | IO_L3N_T0_DQS_AD5N_35 | D1 |

| DDR3_DQS1_P | IO_L9P_T1_DQS_AD7P_35 | K2 |

| DDR3_DQS1_N | IO_L9N_T1_DQS_AD7N_35 | J2 |

| DDR3_DQS2_P | IO_L15P_T2_DQS_35 | M1 |

| DDR3_DQS2_N | IO_L15N_T2_DQS_35 | L1 |

| DDR3_DQS3_P | IO_L21P_T3_DQS_35 | P5 |

| DDR3_DQS3_N | IO_L21N_T3_DQS_35 | P4 |

| DDR3_DQ[0] | IO_L2P_T0_AD12P_35 | C2 |

| DDR3_DQ [1] | IO_L5P_T0_AD13P_35 | G1 |

| DDR3_DQ [2] | IO_L1N_T0_AD4N_35 | A1 |

| DDR3_DQ [3] | IO_L6P_T0_35 | F3 |

| DDR3_DQ [4] | IO_L2N_T0_AD12N_35 | B2 |

| DDR3_DQ [5] | IO_L5N_T0_AD13N_35 | F1 |

| DDR3_DQ [6] | IO_L1P_T0_AD4P_35 | B1 |

| DDR3_DQ [7] | IO_L4P_T0_35 | E2 |

| DDR3_DQ [8] | IO_L11P_T1_SRCC_35 | H3 |

| DDR3_DQ [9] | IO_L11N_T1_SRCC_35 | G3 |

| DDR3_DQ [10] | IO_L8P_T1_AD14P_35 | H2 |

| DDR3_DQ [11] | IO_L10N_T1_AD15N_35 | H5 |

| DDR3_DQ [12] | IO_L7N_T1_AD6N_35 | J1 |

| DDR3_DQ [13] | IO_L10P_T1_AD15P_35 | J5 |

| DDR3_DQ [14] | IO_L7P_T1_AD6P_35 | K1 |

| DDR3_DQ [15] | IO_L12P_T1_MRCC_35 | H4 |

| DDR3_DQ [16] | IO_L18N_T2_35 | L4 |

| DDR3_DQ [17] | IO_L16P_T2_35 | M3 |

| DDR3_DQ [18] | IO_L14P_T2_SRCC_35 | L3 |

| DDR3_DQ [19] | IO_L17N_T2_35 | J6 |

| DDR3_DQ [20] | IO_L14N_T2_SRCC_35 | K3 |

| DDR3_DQ [21] | IO_L17P_T2_35 | K6 |

| DDR3_DQ [22] | IO_L13N_T2_MRCC_35 | J4 |

| DDR3_DQ [23] | IO_L18P_T2_35 | L5 |

| DDR3_DQ [24] | IO_L20N_T3_35 | P1 |

| DDR3_DQ [25] | IO_L19P_T3_35 | N4 |

| DDR3_DQ [26] | IO_L20P_T3_35 | R1 |

| DDR3_DQ [27] | IO_L22N_T3_35 | N2 |

| DDR3_DQ [28] | IO_L23P_T3_35 | M6 |

| DDR3_DQ [29] | IO_L24N_T3_35 | N5 |

| DDR3_DQ [30] | IO_L24P_T3_35 | P6 |

| DDR3_DQ [31] | IO_L22P_T3_35 | P2 |

| DDR3_DM0 | IO_L4N_T0_35 | D2 |

| DDR3_DM1 | IO_L8N_T1_AD14N_35 | G2 |

| DDR3_DM2 | IO_L16N_T2_35 | M2 |

| DDR3_DM3 | IO_L23N_T3_35 | M5 |

| DDR3_A[0] | IO_L11N_T1_SRCC_34 | AA4 |

| DDR3_A[1] | IO_L8N_T1_34 | AB2 |

| DDR3_A[2] | IO_L10P_T1_34 | AA5 |

| DDR3_A[3] | IO_L10N_T1_34 | AB5 |

| DDR3_A[4] | IO_L7N_T1_34 | AB1 |

| DDR3_A[5] | IO_L6P_T0_34 | U3 |

| DDR3_A[6] | IO_L5P_T0_34 | W1 |

| DDR3_A[7] | IO_L1P_T0_34 | T1 |

| DDR3_A[8] | IO_L2N_T0_34 | V2 |

| DDR3_A[9] | IO_L2P_T0_34 | U2 |

| DDR3_A[10] | IO_L5N_T0_34 | Y1 |

| DDR3_A[11] | IO_L4P_T0_34 | W2 |

| DDR3_A[12] | IO_L4N_T0_34 | Y2 |

| DDR3_A[13] | IO_L1N_T0_34 | U1 |

| DDR3_A[14] | IO_L6N_T0_VREF_34 | V3 |

| DDR3_BA[0] | IO_L9N_T1_DQS_34 | AA3 |

| DDR3_BA[1] | IO_L9P_T1_DQS_34 | Y3 |

| DDR3_BA[2] | IO_L11P_T1_SRCC_34 | Y4 |

| DDR3_S0 | IO_L8P_T1_34 | AB3 |

| DDR3_RAS | IO_L12P_T1_MRCC_34 | V4 |

| DDR3_CAS | IO_L12N_T1_MRCC_34 | W4 |

| DDR3_WE | IO_L7P_T1_34 | AA1 |

| DDR3_ODT | IO_L14N_T2_SRCC_34 | U5 |

| DDR3_RESET | IO_L15P_T2_DQS_34 | W6 |

| DDR3_CLK_P | IO_L3P_T0_DQS_34 | R3 |

| DDR3_CLK_N | IO_L3N_T0_DQS_34 | R2 |

| DDR3_CKE | IO_L14P_T2_SRCC_34 | T5 |

څلورمه برخه: QSPI فلش

د FPGA کور بورډ AC7A200 د یو 128Mbit QSPI فلش سره سمبال شوی، او ماډل یې N25Q128 دی، کوم چې د 3.3V CMOS حجم کاروي.tage معیاري. د QSPI فلش د غیر متزلزل طبیعت له امله، دا د سیسټم لپاره د بوټ وسیلې په توګه کارول کیدی شي ترڅو د سیسټم بوټ عکس ذخیره کړي. دا انځورونه په عمده توګه د FPGA بټ شامل دي files، د ARM غوښتنلیک کوډ، د نرم کور غوښتنلیک کوډ او نور د کاروونکي ډاټا files. د SPI FLASH مشخص ماډلونه او اړوند پیرامیټونه په جدول 5-1 کې ښودل شوي.

| موقف | ماډل | ظرفیت | فابریکه |

| U8 | N25Q128 | 128M بټ | نومونیکس |

جدول 5-1: د QSPI فلش مشخصات

QSPI FLASH د FPGA چپ د BANK0 او BANK14 وقف شوي پنونو سره وصل دی. د ساعت پن د BANK0 CCLK0 سره وصل دی، او نور ډیټا او د چپ انتخاب سیګنالونه په ترتیب سره د BANK00 D03~D14 او FCS پنونو سره وصل دي. شکل 5-1 د QSPI فلش هارډویر پیوستون ښیې.

شکل 5-1: د QSPI فلش سکیماتیک

د QSPI فلش پن دندې:

| خالص نوم | د FPGA PIN نوم | FPGA P/N |

| QSPI_CLK | CCLK_0 | L12 |

| QSPI_CS | IO_L6P_T0_FCS_B_14 | T19 |

| QSPI_DQ0 | IO_L1P_T0_D00_MOSI_14 | P22 |

| QSPI_DQ1 | IO_L1N_T0_D01_DIN_14 | R22 |

| QSPI_DQ2 | IO_L2P_T0_D02_14 | P21 |

| QSPI_DQ3 | IO_L2N_T0_D03_14 | R21 |

شکل 5-2: د QSPI فلش په کور بورډ کې

برخه 6: په کور بورډ کې د LED څراغ

په AC3A7 FPGA کور بورډ کې 200 سور LED څراغونه شتون لري، چې یو یې د بریښنا شاخص څراغ (PWR) دی، یو یې د ترتیب LED څراغ (DONE) دی، او یو یې د کاروونکي LED څراغ دی. کله چې اصلي بورډ ځواکمن شي، د بریښنا شاخص به روښانه شي؛ کله چې FPGA تنظیم شي، د ترتیب LED به روښانه شي. د کارونکي LED څراغ د BANK34 IO سره وصل دی ، کارونکي کولی شي د برنامه لخوا رڼا او بند کنټرول کړي. کله چې د IO voltagد کارونکي LED سره وصل دی لوړ دی ، د کارونکي LED روښانه دی. کله چې پیوستون IO voltage ټيټ دی، د کاروونکي LED به مړ شي. د LED رڼا هارډویر پیوستون سکیمیک ډیاګرام په 6-1 شکل کې ښودل شوی:

شکل 6-1: LED څراغونه په کور بورډ سکیمیټ کې

شکل 6-2: په کور بورډ کې د LED څراغونه

د کارونکي LEDs پن دنده

| د سیګنال نوم | د FPGA پن نوم | د FPGA پن نمبر | تفصیل |

| LED1 | IO_L15N_T2_DQS_34 | W5 | د کارونکي LED |

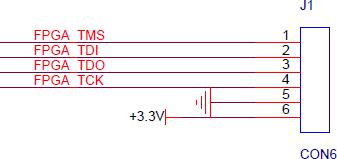

7 برخه: جTAG انٹرفیس

د جيTAG د ازموینې ساکټ J1 د J لپاره په AC7A200 کور بورډ کې خوندي دیTAG ډاونلوډ او ډیبګ کول کله چې اصلي بورډ یوازې کارول کیږي. شکل 7-1 د J سکیماتیک برخه دهTAG بندر، چې پکې TMS، TDI، TDO، TCK شامل دي. ، GND، +3.3V دا شپږ سیګنالونه.

انځور 7-1: JTAG د انٹرفیس سکیماتیک

د جيTAG انٹرفیس J1 په AC7A200 FPGA کور بورډ کې د 6-pin 2.54mm پیچ واحد قطار ټیسټ سوراخ کاروي. که تاسو د J کارولو ته اړتیا لرئTAG په اصلي بورډ کې د ډیبګ کولو لپاره نښلونکی ، تاسو اړتیا لرئ د 6-pin واحد قطار پن سرلیک سولډر کړئ.

7-2 شکل J ښیيTAG انٹرفیس J1 په AC7A200 FPGA کور بورډ کې.

انځور 7-2 JTAG په کور بورډ کې انٹرفیس

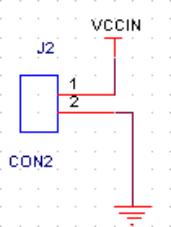

8 برخه: په کور بورډ کې د بریښنا انٹرفیس

د دې لپاره چې د AC7A200 FPGA کور بورډ یوازې کار وکړي ، اصلي بورډ د 2 پن بریښنا رسولو انٹرفیس J2 خوندي دی. که چیرې کاروونکي غواړي د کور بورډ فعالیت په جلا توګه (د کیریر بورډ پرته) ډیبګ کړي، بهرنۍ وسیله اړتیا لري چې کور بورډ ته د بریښنا رسولو لپاره +5V چمتو کړي.

شکل 8-1: په کور بورډ کې د پاور انٹرفیس سکیماتیک

شکل 8-2: په کور بورډ کې د بریښنا انٹرفیس

9 برخه: بورډ ته د بورډ نښلونکو پن دنده

اصلي بورډ د بورډ نښلونکو ته ټولټال څلور لوړ سرعت بورډ لري.

اصلي بورډ د کیریر بورډ سره وصل کولو لپاره څلور 80-pin انټر بورډ نښلونکي کاروي. د FPGA IO بندر د توپیر روټینګ له لارې د څلورو نښلونکو سره وصل دی. د نښلونکو پن فاصله 0.5mm ده، د لوړ سرعت ډیټا مخابراتو لپاره د کیریر بورډ کې د نښلونکو تختو ته داخل کړئ.

بورډ تر بورډ پورې نښلونکي CON1

د 80-pin تخته د بورډ نښلونکو CON1 ته، کوم چې د VCCIN بریښنا رسولو (+5V) سره د نښلولو لپاره کارول کیږي او په کیریر بورډ کې ځمکه، د FPGA نورمال IOs پراخوي. دلته باید یادونه وشي چې د CON15 1 پنونه د BANK34 IO پورټ سره وصل دي ، ځکه چې د BANK34 اړیکه د DDR3 سره وصل ده. له همدې امله، د voltagد دې بانک 34 د ټولو IOs معیار 1.5V دی.

د بورډ نښلونکو CON1 ته د بورډ د پن ګومارنه

| CON1 پن |

جال نوم |

FPGA پن |

والیtage کچه |

CON1 پن |

جال نوم |

FPGA پن |

والیtage کچه |

| پن1 | VCCIN | – | +5V | پن2 | VCCIN | – | +5V |

| پن3 | VCCIN | – | +5V | پن4 | VCCIN | – | +5V |

| پن5 | VCCIN | – | +5V | پن6 | VCCIN | – | +5V |

| پن7 | VCCIN | – | +5V | پن8 | VCCIN | – | +5V |

| پن9 | GND | – | ځمکه | پن10 | GND | – | ځمکه |

| پن11 | NC | – | NC | پن12 | NC | – | NC |

| پن13 | NC | – | NC | پن14 | NC | – | NC |

| پن15 | NC | – | NC | پن16 | B13_L4_P | AA15 | 3.3V |

| پن17 | NC | – | NC | پن18 | B13_L4_N | AB15 | 3.3V |

| پن19 | GND | – | ځمکه | پن20 | GND | – | ځمکه |

| پن21 | B13_L5_P | Y13 | 3.3V | پن22 | B13_L1_P | Y16 | 3.3V |

| پن23 | B13_L5_N | AA14 | 3.3V | پن24 | B13_L1_N | AA16 | 3.3V |

| پن25 | B13_L7_P | AB11 | 3.3V | پن26 | B13_L2_P | AB16 | 3.3V |

| پن27 | B13_L7_P | AB12 | 3.3V | پن28 | B13_L2_N | AB17 | 3.3V |

| پن29 | GND | – | ځمکه | پن30 | GND | – | ځمکه |

| پن31 | B13_L3_P | AA13 | 3.3V | پن32 | B13_L6_P | W14 | 3.3V |

| پن33 | B13_L3_N | AB13 | 3.3V | پن34 | B13_L6_N | Y14 | 3.3V |

| پن35 | B34_L23_P | Y8 | 1.5V | پن36 | B34_L20_P | AB7 | 1.5V |

| پن37 | B34_L23_N | Y7 | 1.5V | پن38 | B34_L20_N | AB6 | 1.5V |

| پن39 | GND | – | ځمکه | پن40 | GND | – | ځمکه |

| پن41 | B34_L18_N | AA6 | 1.5V | پن42 | B34_L21_N | V8 | 1.5V |

| پن43 | B34_L18_P | Y6 | 1.5V | پن44 | B34_L21_P | V9 | 1.5V |

| پن45 | B34_L19_P | V7 | 1.5V | پن46 | B34_L22_P | AA8 | 1.5V |

| پن47 | B34_L19_N | W7 | 1.5V | پن48 | B34_L22_N | AB8 | 1.5V |

| پن49 | GND | – | ځمکه | پن50 | GND | – | ځمکه |

| پن51 | XADC_VN | M9 | انلاګ | پن52 | NC | ||

| پن53 | XADC_VP | L10 | انلاګ | پن54 | B34_L25 | U7 | 1.5V |

| پن55 | NC | – | NC | پن56 | B34_L24_P | W9 | 1.5V |

| پن57 | NC | – | NC | پن58 | B34_L24_N | Y9 | 1.5V |

| پن59 | GND | – | ځمکه | پن60 | GND | – | ځمکه |

| پن61 | B16_L1_N | F14 | 3.3V | پن62 | NC | – | NC |

| پن63 | B16_L1_P | F13 | 3.3V | پن64 | NC | – | NC |

| پن65 | B16_L4_N | E14 | 3.3V | پن66 | NC | – | NC |

| پن67 | B16_L4_P | E13 | 3.3V | پن68 | NC | – | NC |

| پن69 | GND | – | ځمکه | پن70 | GND | – | ځمکه |

| پن71 | B16_L6_N | D15 | 3.3V | پن72 | NC | – | NC |

| پن73 | B16_L6_P | D14 | 3.3V | پن74 | NC | – | NC |

| پن75 | B16_L8_P | C13 | 3.3V | پن76 | NC | – | NC |

| پن77 | B16_L8_N | B13 | 3.3V | پن78 | NC | – | NC |

| پن79 | NC | – | NC | پن80 | NC | – | NC |

شکل 9-1: په کور بورډ کې بورډ ته بورډ نښلونکي CON1

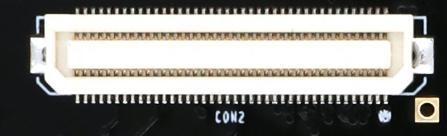

بورډ تر بورډ پورې نښلونکي CON2

د 80-pin ښځینه پیوستون سرلیک CON2 د FPGA د BANK13 او BANK14 نورمال IO پراخولو لپاره کارول کیږي. د ټوکtagد دواړو بانکونو معیارونه 3.3V دي.

د بورډ نښلونکو CON2 ته د بورډ د پن ګومارنه

| CON2 پن |

جال نوم |

FPGA پن |

والیtage کچه |

CON2 پن |

جال نوم |

FPGA پن |

والیtage کچه |

| پن1 | B13_L16_P | W15 | 3.3V | پن2 | B14_L16_P | V17 | 3.3V |

| پن3 | B13_L16_N | W16 | 3.3V | پن4 | B14_L16_N | W17 | 3.3V |

| پن5 | B13_L15_P | T14 | 3.3V | پن6 | B13_L14_P | U15 | 3.3V |

| پن7 | B13_L15_N | T15 | 3.3V | پن8 | B13_L14_N | V15 | 3.3V |

| پن9 | GND | – | ځمکه | پن10 | GND | – | ځمکه |

| پن11 | B13_L13_P | V13 | 3.3V | پن12 | B14_L10_P | AB21 | 3.3V |

| پن13 | B13_L13_N | V14 | 3.3V | پن14 | B14_L10_N | AB22 | 3.3V |

| پن15 | B13_L12_P | W11 | 3.3V | پن16 | B14_L8_N | AA21 | 3.3V |

| پن17 | B13_L12_N | W12 | 3.3V | پن18 | B14_L8_P | AA20 | 3.3V |

| پن19 | GND | – | ځمکه | پن20 | GND | – | ځمکه |

| پن21 | B13_L11_P | Y11 | 3.3V | پن22 | B14_L15_N | AB20 | 3.3V |

| پن23 | B13_L11_N | Y12 | 3.3V | پن24 | B14_L15_P | AA19 | 3.3V |

| پن25 | B13_L10_P | V10 | 3.3V | پن26 | B14_L17_P | AA18 | 3.3V |

| پن27 | B13_L10_N | W10 | 3.3V | پن28 | B14_L17_N | AB18 | 3.3V |

| پن29 | GND | – | ځمکه | پن30 | GND | – | ځمکه |

| پن31 | B13_L9_N | AA11 | 3.3V | پن32 | B14_L6_N | T20 | 3.3V |

| پن33 | B13_L9_P | AA10 | 3.3V | پن34 | B13_IO0 | Y17 | 3.3V |

| پن35 | B13_L8_N | AB10 | 3.3V | پن36 | B14_L7_N | W22 | 3.3V |

| پن37 | B13_L8_P | AA9 | 3.3V | پن38 | B14_L7_P | W21 | 3.3V |

| پن39 | GND | – | ځمکه | پن40 | GND | – | ځمکه |

| پن41 | B14_L11_N | V20 | 3.3V | پن42 | B14_L4_P | T21 | 3.3V |

| پن43 | B14_L11_P | U20 | 3.3V | پن44 | B14_L4_N | U21 | 3.3V |

| پن45 | B14_L14_N | V19 | 3.3V | پن46 | B14_L9_P | Y21 | 3.3V |

| پن47 | B14_L14_P | V18 | 3.3V | پن48 | B14_L9_N | Y22 | 3.3V |

| پن49 | GND | – | ځمکه | پن50 | GND | – | ځمکه |

| پن51 | B14_L5_N | R19 | 3.3V | پن52 | B14_L12_N | W20 | 3.3V |

| پن53 | B14_L5_P | P19 | 3.3V | پن54 | B14_L12_P | W19 | 3.3V |

| پن55 | B14_L18_N | U18 | 3.3V | پن56 | B14_L13_N | Y19 | 3.3V |

| پن57 | B14_L18_P | U17 | 3.3V | پن58 | B14_L13_P | Y18 | 3.3V |

| پن59 | GND | – | ځمکه | پن60 | GND | – | ځمکه |

| پن61 | B13_L17_P | T16 | 3.3V | پن62 | B14_L3_N | V22 | 3.3V |

| پن63 | B13_L17_N | U16 | 3.3V | پن64 | B14_L3_P | U22 | 3.3V |

| پن65 | B14_L21_N | P17 | 3.3V | پن66 | B14_L20_N | T18 | 3.3V |

| پن67 | B14_L21_P | N17 | 3.3V | پن68 | B14_L20_P | R18 | 3.3V |

| پن69 | GND | – | ځمکه | پن70 | GND | – | ځمکه |

| پن71 | B14_L22_P | P15 | 3.3V | پن72 | B14_L19_N | R14 | 3.3V |

| پن73 | B14_L22_N | R16 | 3.3V | پن74 | B14_L19_P | P14 | 3.3V |

| پن75 | B14_L24_N | R17 | 3.3V | پن76 | B14_L23_P | N13 | 3.3V |

| پن77 | B14_L24_P | P16 | 3.3V | پن78 | B14_L23_N | N14 | 3.3V |

| پن79 | B14_IO0 | P20 | 3.3V | پن80 | B14_IO25 | N15 | 3.3V |

شکل 9-2: په کور بورډ کې بورډ ته بورډ نښلونکي CON2

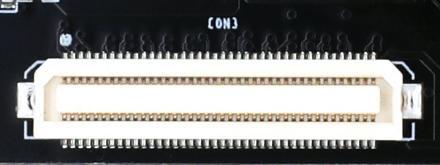

بورډ تر بورډ پورې نښلونکي CON3

د 80 پن نښلونکی CON3 د FPGA د BANK15 او BANK16 نورمال IO غزولو لپاره کارول کیږي. سربیره پردې، څلور JTAG سیګنالونه هم د CON3 نښلونکي له لارې د کیریر بورډ سره وصل دي. د ټوکtagد BANK15 او BANK16 معیارونه د LDO چپ لخوا تنظیم کیدی شي. ډیفالټ نصب شوی LDO 3.3V دی. که تاسو غواړئ نور معیاري کچې تولید کړئ، تاسو کولی شئ دا د مناسب LDO سره بدل کړئ.

د بورډ نښلونکو CON3 ته د بورډ د پن ګومارنه

| CON3 پن |

جال نوم |

FPGA پن |

والیtage کچه |

CON3 پن |

جال نوم |

FPGA پن |

والیtage کچه |

| پن1 | B15_IO0 | J16 | 3.3V | پن2 | B15_IO25 | M17 | 3.3V |

| پن3 | B16_IO0 | F15 | 3.3V | پن4 | B16_IO25 | F21 | 3.3V |

| پن5 | B15_L4_P | G17 | 3.3V | پن6 | B16_L21_N | A21 | 3.3V |

| پن7 | B15_L4_N | G18 | 3.3V | پن8 | B16_L21_P | B21 | 3.3V |

| پن9 | GND | – | ځمکه | پن10 | GND | – | ځمکه |

| پن11 | B15_L2_P | G15 | 3.3V | پن12 | B16_L23_P | E21 | 3.3V |

| پن13 | B15_L2_N | G16 | 3.3V | پن14 | B16_L23_N | D21 | 3.3V |

| پن15 | B15_L12_P | J19 | 3.3V | پن16 | B16_L22_P | E22 | 3.3V |

| پن17 | B15_L12_N | H19 | 3.3V | پن18 | B16_L22_N | D22 | 3.3V |

| پن19 | GND | – | ځمکه | پن20 | GND | – | ځمکه |

| پن21 | B15_L11_P | J20 | 3.3V | پن22 | B16_L24_P | G21 | 3.3V |

| پن23 | B15_L11_N | J21 | 3.3V | پن24 | B16_L24_N | G22 | 3.3V |

| پن25 | B15_L1_N | G13 | 3.3V | پن26 | B15_L8_N | G20 | 3.3V |

| پن27 | B15_L1_P | H13 | 3.3V | پن28 | B15_L8_P | H20 | 3.3V |

| پن29 | GND | – | ځمکه | پن30 | GND | – | ځمکه |

| پن31 | B15_L5_P | J15 | 3.3V | پن32 | B15_L7_N | H22 | 3.3V |

| پن33 | B15_L5_N | H15 | 3.3V | پن34 | B15_L7_P | J22 | 3.3V |

| پن35 | B15_L3_N | H14 | 3.3V | پن36 | B15_L9_P | K21 | 3.3V |

| پن37 | B15_L3_P | J14 | 3.3V | پن38 | B15_L9_N | K22 | 3.3V |

| پن39 | GND | – | ځمکه | پن40 | GND | – | ځمکه |

| پن41 | B15_L19_P | K13 | 3.3V | پن42 | B15_L15_N | M22 | 3.3V |

| پن43 | B15_L19_N | K14 | 3.3V | پن44 | B15_L15_P | N22 | 3.3V |

| پن45 | B15_L20_P | M13 | 3.3V | پن46 | B15_L6_N | H18 | 3.3V |

| پن47 | B15_L20_N | L13 | 3.3V | پن48 | B15_L6_P | H17 | 3.3V |

| پن49 | GND | – | ځمکه | پن50 | GND | – | ځمکه |

| پن51 | B15_L14_P | L19 | 3.3V | پن52 | B15_L13_N | K19 | 3.3V |

| پن53 | B15_L14_N | L20 | 3.3V | پن54 | B15_L13_P | K18 | 3.3V |

| پن55 | B15_L21_P | K17 | 3.3V | پن56 | B15_L10_P | M21 | 3.3V |

| پن57 | B15_L21_N | J17 | 3.3V | پن58 | B15_L10_N | L21 | 3.3V |

| پن59 | GND | – | ځمکه | پن60 | GND | – | ځمکه |

| پن61 | B15_L23_P | L16 | 3.3V | پن62 | B15_L18_P | N20 | 3.3V |

| پن63 | B15_L23_N | K16 | 3.3V | پن64 | B15_L18_N | M20 | 3.3V |

| پن65 | B15_L22_P | L14 | 3.3V | پن66 | B15_L17_N | N19 | 3.3V |

| پن67 | B15_L22_N | L15 | 3.3V | پن68 | B15_L17_P | N18 | 3.3V |

| پن69 | GND | – | ځمکه | پن70 | GND | – | ځمکه |

| پن71 | B15_L24_P | M15 | 3.3V | پن72 | B15_L16_P | M18 | 3.3V |

| پن73 | B15_L24_N | M16 | 3.3V | پن74 | B15_L16_N | L18 | 3.3V |

| پن75 | NC | – | پن76 | NC | – | ||

| پن77 | FPGA_TCK | V12 | 3.3V | پن78 | FPGA_TDI | R13 | 3.3V |

| پن79 | FPGA_TDO | U13 | 3.3V | پن80 | FPGA_TMS | T13 | 3.3V |

شکل 9-3: په کور بورډ کې بورډ ته بورډ نښلونکي CON3

بورډ تر بورډ پورې نښلونکي CON4

د 80-Pin نښلونکی CON4 د نورمال IO او GTP لوړ سرعت ډیټا او د FPGA BANK16 ساعت سیګنالونو غزولو لپاره کارول کیږي. د ټوکtagد BANK16 د IO پورټ معیار د LDO چپ لخوا تنظیم کیدی شي. ډیفالټ نصب شوی LDO 3.3V دی. که کاروونکي غواړي نور معیاري کچې تولید کړي، دا د مناسب LDO لخوا بدلیدلی شي. د GTP د لوړ سرعت ډیټا او د ساعت سیګنالونه په اصلي بورډ کې په کلکه توپیر لري. د ډیټا لینونه په اوږدوالي کې مساوي دي او په یو ټاکلي وقفه کې ساتل کیږي ترڅو د سیګنال مداخلې مخه ونیسي.

د بورډ نښلونکو CON4 ته د بورډ د پن ګومارنه

| CON4 پن |

جال نوم |

FPGA پن |

والیtage کچه |

CON4 پن |

جال نوم |

FPGA پن |

والیtage کچه |

| پن1 | NC | – | – | پن2 | – | – | |

| پن3 | NC | – | – | پن4 | – | – | |

| پن5 | NC | – | – | پن6 | – | – | |

| پن7 | NC | – | – | پن8 | – | – | |

| پن9 | GND | – | ځمکه | پن10 | GND | – | ځمکه |

| پن11 | NC | – | – | پن12 | MGT_TX2_P | B6 | توپیر |

| پن13 | NC | – | – | پن14 | MGT_TX2_N | A6 | توپیر |

| پن15 | GND | – | ځمکه | پن16 | GND | – | ځمکه |

| پن17 | MGT_TX3_P | D7 | توپیر | پن18 | MGT_RX2_P | B10 | توپیر |

| پن19 | MGT_TX3_N | C7 | توپیر | پن20 | MGT_RX2_N | A10 | توپیر |

| پن21 | GND | – | ځمکه | پن22 | GND | – | ځمکه |

| پن23 | MGT_RX3_P | D9 | توپیر | پن24 | MGT_TX0_P | B4 | توپیر |

| پن25 | MGT_RX3_N | C9 | توپیر | پن26 | MGT_TX0_N | A4 | توپیر |

| پن27 | GND | – | ځمکه | پن28 | GND | – | ځمکه |

| پن29 | MGT_TX1_P | D5 | توپیر | پن30 | MGT_RX0_P | B8 | توپیر |

| پن31 | MGT_TX1_N | C5 | توپیر | پن32 | MGT_RX0_N | A8 | توپیر |

| پن33 | GND | – | ځمکه | پن34 | GND | – | ځمکه |

| پن35 | MGT_RX1_P | D11 | توپیر | پن36 | MGT_CLK1_P | F10 | توپیر |

| پن37 | MGT_RX1_N | C11 | توپیر | پن38 | MGT_CLK1_N | E10 | توپیر |

| پن39 | GND | – | ځمکه | پن40 | GND | – | ځمکه |

| پن41 | B16_L5_P | E16 | 3.3V | پن42 | B16_L2_P | F16 | 3.3V |

| پن43 | B16_L5_N | D16 | 3.3V | پن44 | B16_L2_N | E17 | 3.3V |

| پن45 | B16_L7_P | B15 | 3.3V | پن46 | B16_L3_P | C14 | 3.3V |

| پن47 | B16_L7_N | B16 | 3.3V | پن48 | B16_L3_N | C15 | 3.3V |

| پن49 | GND | – | ځمکه | پن50 | GND | – | ځمکه |

| پن51 | B16_L9_P | A15 | 3.3V | پن52 | B16_L10_P | A13 | 3.3V |

| پن53 | B16_L9_N | A16 | 3.3V | پن54 | B16_L10_N | A14 | 3.3V |

| پن55 | B16_L11_P | B17 | 3.3V | پن56 | B16_L12_P | D17 | 3.3V |

| پن57 | B16_L11_N | B18 | 3.3V | پن58 | B16_L12_N | C17 | 3.3V |

| پن59 | GND | – | ځمکه | پن60 | GND | – | ځمکه |

| پن61 | B16_L13_P | C18 | 3.3V | پن62 | B16_L14_P | E19 | 3.3V |

| پن63 | B16_L13_N | C19 | 3.3V | پن64 | B16_L14_N | D19 | 3.3V |

| پن65 | B16_L15_P | F18 | 3.3V | پن66 | B16_L16_P | B20 | 3.3V |

| پن67 | B16_L15_N | E18 | 3.3V | پن68 | B16_L16_N | A20 | 3.3V |

| پن69 | GND | – | ځمکه | پن70 | GND | – | ځمکه |

| پن71 | B16_L17_P | A18 | 3.3V | پن72 | B16_L18_P | F19 | 3.3V |

| پن73 | B16_L17_N | A19 | 3.3V | پن74 | B16_L18_N | F20 | 3.3V |

| پن75 | B16_L19_P | D20 | 3.3V | پن76 | B16_L20_P | C22 | 3.3V |

| پن77 | B16_L19_N | C20 | 3.3V | پن78 | B16_L20_N | B22 | 3.3V |

| پن79 | NC | – | پن80 | NC | – |

شکل 9-4: په کور بورډ کې بورډ ته بورډ نښلونکي CON4

10 برخه: د بریښنا رسول

د AC7A200 FPGA کور بورډ د کیریر بورډ له لارې د DC5V لخوا پرمخ وړل کیږي، او دا د مینی USB انٹرفیس لخوا ځواکمن کیږي کله چې دا یوازې کارول کیږي. مهرباني وکړئ محتاط اوسئ چې د مینی USB او کیریر بورډ لخوا په ورته وخت کې بریښنا مه ورکوئ ترڅو د زیان مخه ونیول شي. په تخته کې د بریښنا رسولو ډیزاین ډیاګرام په 10-1 شکل کې ښودل شوی.

شکل 10-1: په کور بورډ سکیمیک کې د بریښنا رسول

اصلي تخته د +5V لخوا پرمخ وړل کیږي او د درې DC/DC بریښنا رسولو چپ TLV3.3RGT له لارې +1.5V، +1.8V، +1.0V، +62130V څلور طرفه بریښنا رسولو ته بدلیږي. د +1.0V اوسنی جریان تر 6A پورې کیدی شي، او نور درې د تولید جریان تر 3A پورې وي. VCCIO د یو LDOSPX3819M5-3-3 لخوا رامینځته شوی. VCCIO په عمده توګه د FPGA BANK15 او BANK16 ته بریښنا رسوي. کاروونکي کولی شي د BANK15,16 IO مختلف حجم ته بدل کړيtagد دوی د LDO چپ ځای په ځای کولو سره معیارونه. 1.5V د VTT او VREF حجم تولیدويtagد TI د TPS3 له لارې د DDR51200 لخوا اړین دي. د GTP ټرانسیور لپاره د MGTAVTT او MGTAVCC 1.8V بریښنا رسول د TI د TPS74801 چپ لخوا رامینځته شوی. د هرې بریښنا ویش دندې په لاندې جدول کې ښودل شوي:

| د بریښنا رسول | فعالیت |

| +1.0V | د FPGA کور حجمtage |

| +1.8V | د FPGA معاون والیومtage، TPS74801 بریښنا رسول |

| +3.3V | د بانک 0، بانک 13 او بانک 14 د FPGA VCCIO، QSIP فلش، د ساعت کرسټال |

| +1.5V | د FPGA DDR3، Bank34 او Bank35 |

| VREF,VTT(+0.75V) | DDR3 |

| CCIP(+3.3V) | FPGA بانک 15، بانک 16 |

| MGTAVTT(+1.2V) | د FPGA GTP لیږدونکي بانک 216 |

| MGTVCC(+1.0V) | د FPGA GTP لیږدونکي بانک 216 |

ځکه چې د آرټیکس-7 FPGA بریښنا رسولو د بریښنا پر ترتیب ترتیب اړتیا لري، د سرکټ ډیزاین کې، موږ د چپ بریښنا اړتیاو سره سم ډیزاین کړی، او د بریښنا انډول 1.0V->1.8V->(1.5) دی. V, 3.3V, VCCIO) او 1.0V-> MGTAVCC -> MGTAVTT، د سرکټ ډیزاین ترڅو د چپ نورمال عملیات یقیني کړي.

د AC7A200 FPGA کور بورډ کې د بریښنا سرکټ په 10-2 شکل کې ښودل شوی:

شکل 10-2: په AC7A200 FPGA کور بورډ کې د بریښنا رسول

11 برخه: د اندازې اندازه

شکل 11-1: AC7A200 FPGA کور بورډ (پورته View)

شکل 11-2: AC7A200 FPGA کور بورډ (لاندې View)

اسناد / سرچینې

|

ALINX AC7A200 ARTIX-7 FPGA پراختیایی بورډ [pdf] د کارونکي لارښود AC7A200 ARTIX-7 FPGA پراختیایی بورډ، AC7A200، ARTIX-7 FPGA پراختیایی بورډ، د FPGA پراختیایی بورډ، پراختیایی بورډ، بورډ |